# DELPHON

Merging Innovative Technologies

# Increasing the Role of Probe from Lab to Fab: The Mission of Critical Data

### Jerry Broz, PhD

VP of Business Development & Strategic Marketing, Delphon Industries, LLC. General Chair of SWTest Conferences

A Delphon Company

Gel-Pak ТоиснМакк UltraTape

Gel-Pak | Delphon | At-A-Glance

Merging Innovative Technologies

**DELPHON**

- Delphon Industries develops and delivers highly engineered materials for the semiconductor, medical, photonics, and electronic industries.

- High volume, ISO 9001:2015 certified facilities are headquartered in Hayward, CA with operations in Wilsonville, OR, and Johor, Malaysia.

- With 90,000 sq. ft. and several ISO Class 7 cleanrooms, Delphon Divisions have been producing innovative products since 1980.

- Over 1,000 global customers, ranging from Fortune 500 companies to startups to universities labs rely on Delphon expertise and innovation.

- Trusted by numerous industries to handle, transport, or process small, high value devices without risk of damage.

### Gel-Рак ТоиснМакк UltraTape

# **Evolving with Semiconductor Industry Trends**

Gel-Pak has continuously innovated to align with emerging trends in the semiconductor industry to address demanding applications.

| 1980                                                                                                                | 1990                                                                                                                              | 2000                                                                                                                                          | Mid 2000                                                                                                              | TODAY                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Beam Lead Diode was<br>introduced to improve high-<br>frequency performance<br>and facilitate automated<br>assembly | Multi-Chip Modules<br>introduced to enhance<br>signal performance, reduce<br>costs, improve flexibility,<br>and reduce footprint. | Thinner compound<br>semiconductors improve<br>performance, reduce power<br>consumption, and enable<br>miniaturization                         | Miniaturization trends<br>introduce semiconductor<br>reliability challenges and<br>quality standards are<br>elevated. | Innovations in heterogenous<br>packaging to overcome Moore's<br>law drives advancements in<br>semiconductor test.      |

| GEL-BOX                                                                                                             | VACUUM RELEASE<br>(VR) TECHNOLOGY                                                                                                 | LARGE FORMAT VR<br>NANO DEVICE TRAYS                                                                                                          | VERTEC <sup>®</sup><br>CARRIERS                                                                                       | GEL-PROBE AND BTXF                                                                                                     |

| Gel-Pak partners with HP to<br>create solutions for<br>shipping beam lead diodes<br>Gel-Box was born                | Gel-Pak launches patented<br>Vacuum Release Tray to<br>drive Multi-Chip Module<br>assembly efficiency.                            | Gel-Pak introduces large<br>format carriers for thin<br>compound semi wafers and<br>substrates up to 300 mm.<br>NDT products for thin, ultra- | Gel-Pak static dissipative,<br>silicone-free Vertec carriers<br>are introduced.                                       | Gel-Pak introduces<br>textured device carrier ideal<br>for in-process handling<br>during heterogeneous<br>integration. |

|                                                                                                                     |                                                                                                                                   | small devices > 25 µm.                                                                                                                        |                                                                                                                       | Gel-Probe products                                                                                                     |

improve wafer yield and

reduce cost of test.

A Delphon Company

# **Gel-Pak Innovations Drive OEE**

#### ELASTOMER PROBE CARD CLEANING FILMS

#### Gel-Probe Card Cleaning

- Custom coating of highly engineered elastomer films for semiconductor applications.

- Customizable probecard cleaning wafer and cleaning sheet applications.

#### SMALL DIE SHIPPING & HANDLING

#### Vacuum Release Carriers

- Automated pick & place applications for bare die and devices ranging from <250 micron to 75mm in size.

- Handling small components or large assembled modules.

• Suitable for transport and handling MEMs Probes

#### DIE WAFER & PANEL SHIPPING & HANDLING

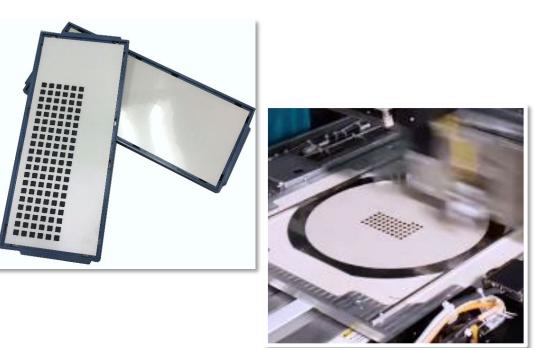

#### Large Substrate Vacuum Release Carriers™

- Shipping and handling full or partial wafers, panels, and OTHER substrates from 75mm to 450mm.

- Suitable for KGD, singulated die, and filn frame loaded devices.

#### UNIVERSAL & POCKETLESS CARRIERS

#### Textured Device Carrier Products

- Pocketless \carriers and transport products for KGD and other devices

- Universal Fixture for device handling inprocess, singulated die testing, and shipping.

### Gel-Pak ТоиснМакк UltraTape

ρ

A Delphon Company

Gel-Pak ТоиснМакк UltraTape

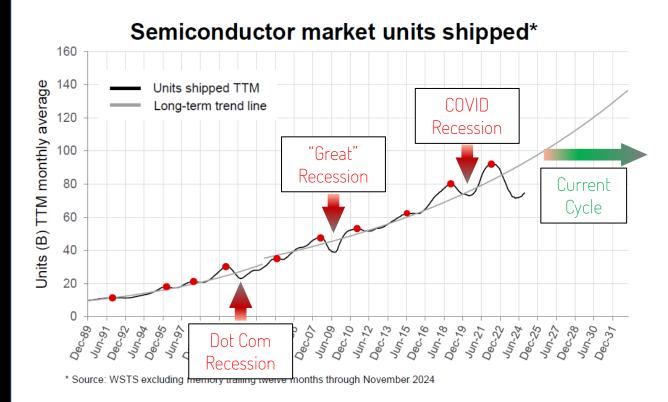

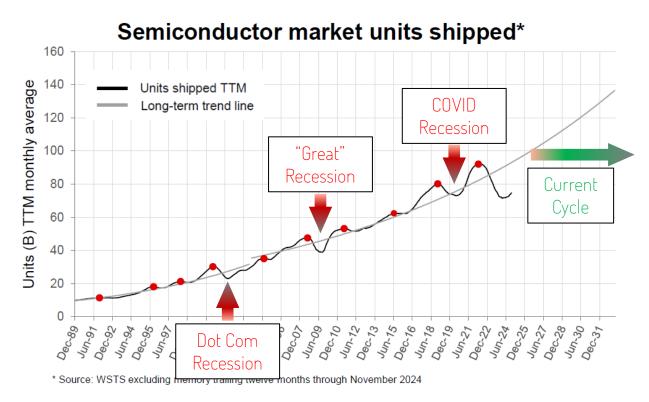

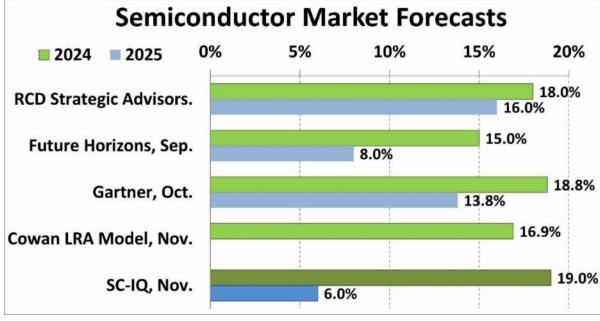

# Semiconductor Is Notoriously Cyclical

#### Factors in play:

- Third-quarter 2024 saw a semiconductor market growth of \$166 billion, marking a 10.7% increase from the previous quarter and 23.2% year-over-year growth.

- Outlook for Q4 2024 indicates diverging trends, with strong Al-driven demand for data centers boosting revenues for companies like Nvidia, while automotive is forecasting declines.

- 2025 projections show a mixed outlook with continued growth in AI, moderate growth in PCs/smartphones, and a weak automotive market, alongside potential consumer demand impacts from higher tariffs.

Source: Texas Instruments Investor Day - 2024

# Semiconductor Is Notoriously Cyclical

#### Factors in play:

#### Source: Texas Instruments Investor Day - 2024

A Delphon Company

Gel-Pak ТоиснМакк UltraTape

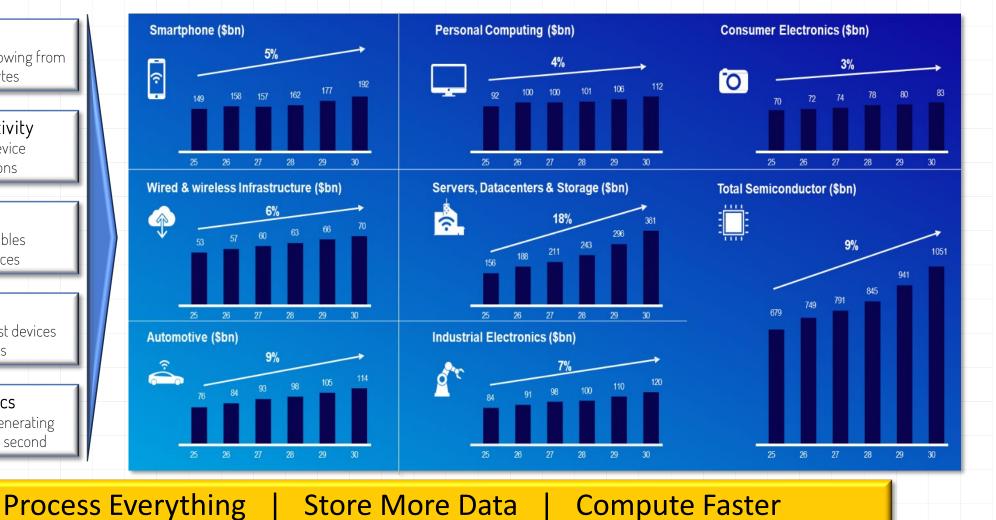

# **Market Drivers**

Data Cloud and Al High-Capacity Storage, and HPC growing from 5 Zettabytes to > 40 Zettabytes

> 5G and Massive Connectivity More than 1.1 billion smart-device and high-volume connections

Smart Devices More than 250 million wearables and high-performance devices

Internet of Things 50B connected devices of low-cost devices and massive data volumes

Automotive Electronics 89 million connected cars each generating and processing > 1GB of data per second

Source: A. Harchandani, ASML Investor Day 2024

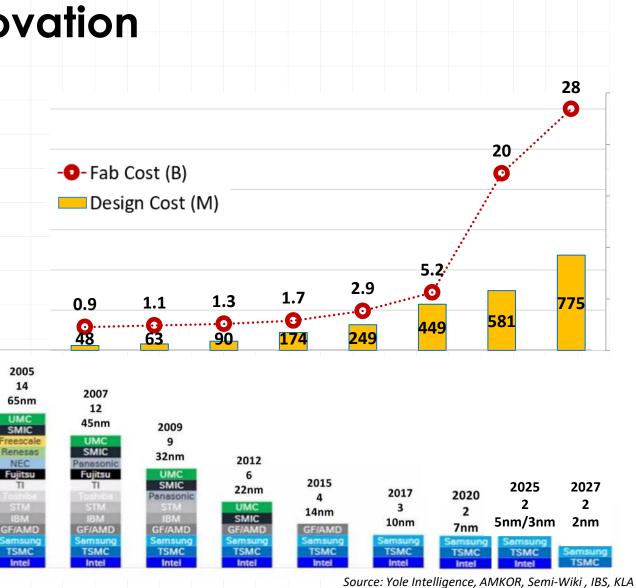

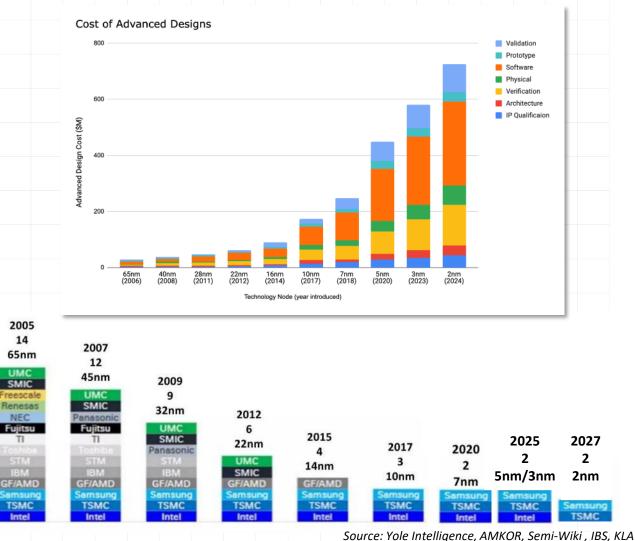

# **Costs of Accelerating Innovation**

- Costs associated with design, introduction, and fab of new products for nodes below 22nm has increased almost 8X.

- "Monolithic" approach has extremely high development costs and precludes all but two global IDMs from pursuing this path.

- Heterogeneous integration and advanced packaging can use "best-in-class technologies" from multiple sources to advance performance trends at acceptable costs.

• Reuse of various designs can significantly lower costs when using standardized IP.

Gel-Pak

**UltraTape**

**TOUCHMARK**

# **Costs of Accelerating Innovation**

14

TI

- Costs associated with design, introduction, and fab of new products for nodes below 22nm has increased almost 8X.

- "Monolithic" approach has extremely high development costs and precludes all but two global IDMs from pursuing this path.

- Heterogeneous integration and advanced packaging can use "best-in-class technologies" from multiple sources to advance performance trends at acceptable costs.

Reuse of various designs can significantly lower costs when using standardized IP.

# **Consumer Demand**

Data Cloud and Al High-Capacity Storage, and HPC growing from 5 Zettabytes to > 40 Zettabytes

> 5G and Massive Connectivity More than 1.1 billion smart-device and high-volume connections

Smart Devices More than 250 million wearables and high-performance devices

Internet of Things 50B connected devices of low-cost devices and massive data volumes

Automotive Electronics 89 million connected cars each generating and processing > 1GB of data per second

Source: S. Kirshnamoorthy, IEEE ITC 2024

**TOUCHMARK**

Gel-Pak

UltraTape

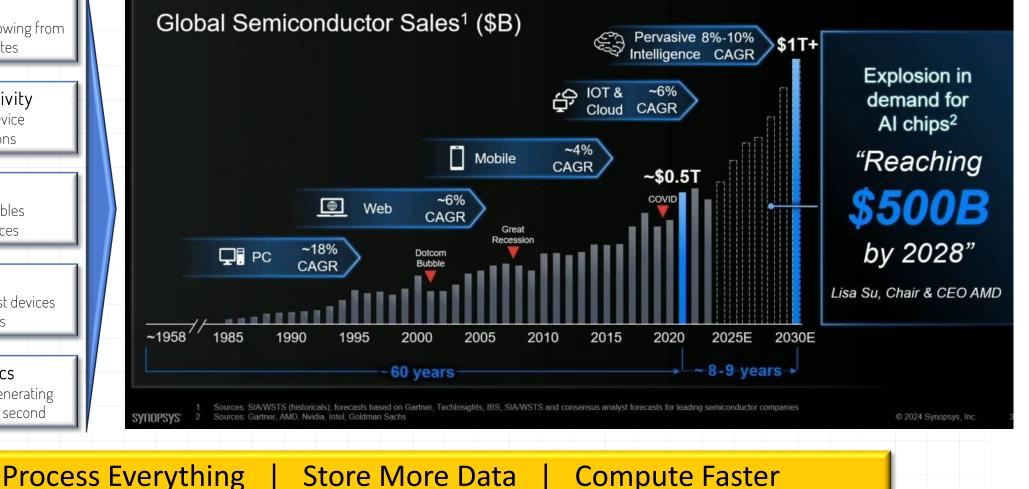

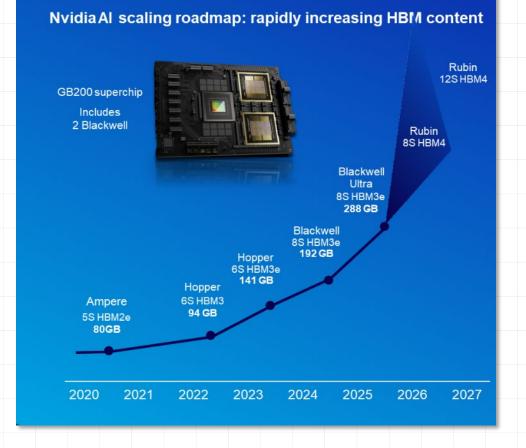

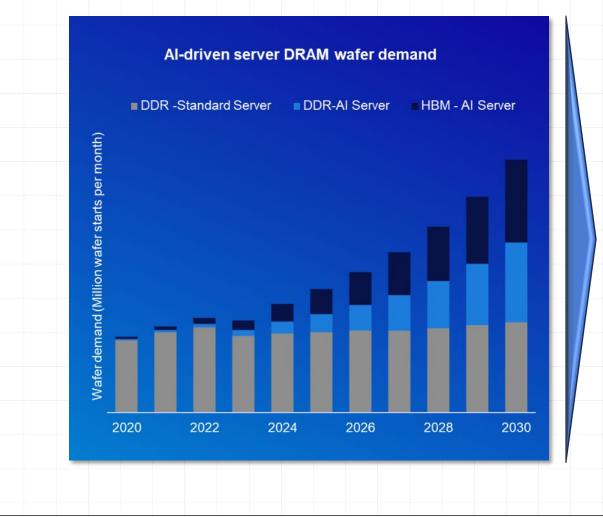

# **Demand for HBM & Al**

### • Global semiconductor sales hit \$627.6B in 2024

• Increase of 19.1% over 2023 total of \$526.8B.

### Memory had 71.8% revenue growth in 2024.

- Memory's share as a percentage of total semiconductor sales increased to 25.2% in 2024.

- DRAM revenue improved 75.4% in 2024 while NAND revenue increased 75.7% year-over-year.

### • Nonmemory revenue increased 6.9% in 2024.

- Nonmemory accounted for 74.8% of total semiconductor revenue in 2024.

- High-bandwidth memory (HBM) production contributed significantly to DRAM revenues.

- HBM was 19.2% of DRAM Revenue in 2025 (up 13.6% over 2024)

- HBM revenue is estimated to increase 66.3% in 2025, reaching \$19.8B.

Source: ASML 2024 Investors, Yole Intelligence, Semi-Wiki, IBS

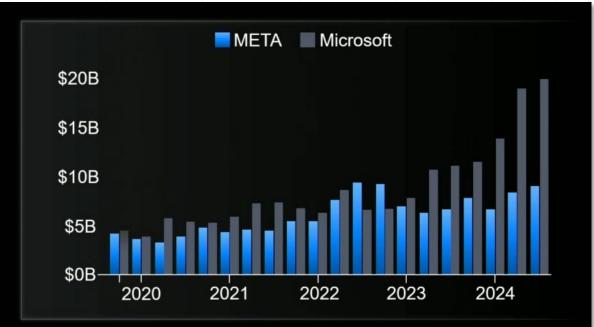

## **AI Demand & Expenditures**

Source: Company reports/ Yahoo Finance Yahoo Finance - Microsoft and Meta report on different fiscal calendars

Memory and AI semiconductors will drive near-term growth, with HBM projected to account for an increasing share of DRAM revenue, reaching 19.2% in 2025.

Source: ASML 2024 Investors, S. Kirshnamoorthy, IEEE ITC 2024

### A Delphon Company

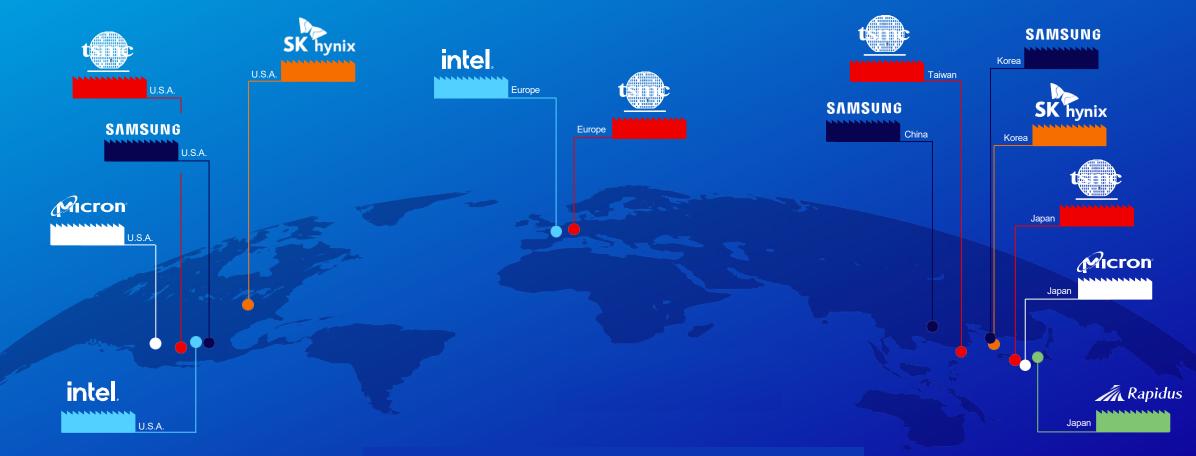

# Wafer capacity | Global Investments

| US CHIPS a | nd Science Act   |

|------------|------------------|

|            | • \$52bn investm |

|            | • Tax credits    |

- \$52bn investment

- Tax credits

- Intel \$40B

- TI \$41B

- Micron \$35B

- Wolfspeed \$5B

#### **European Chips Act**

- \$48bn investment

- Tax credits

- Infineon \$6B

- Bosch \$3B

- ASML \$0.5B/yr

#### SOUTH KOREA-Semi Strategy

- Government support via tax credits and loans

- Samsung \$230B

- SK Hynix \$11B

#### CHINA "Big Fund" Phase 3

• \$48bn central government investment

#### **INDIA Semiconductor Mission**

\$10bn government investment

## **Government & Industry** Investment

#### **JAPAN Strategy for Semi**

- \$26bn investment

- Tax credits

- SONY \$7B

$\overset{}{\otimes}$

#### **TAIWAN Chip-Based Industrial Innovation Program**

- \$9bn investment

- Tax credits

- TSMC \$100B

- UMC \$15B

Source: SEMI.org, Public announcements, FTI Consulting analysis and ASML analysis; Note: The overview is not exhaustive

UltraTape **TOUCHMARK** Gel-Pak 15

# Wafer capacity | Global Investments

Source: SEMI.org, Public announcements, FTI Consulting analysis and ASML analysis; Note: The overview is not exhaustive

# Wafer capacity | Global Investments

### Leading Edge Non-Memory

Source: SEMI.org, Public announcements, FTI Consulting analysis and ASML analysis; Note: The overview is not exhaustive

A Delphon Company

Gel-Pak ТоиснМакк UltraTape

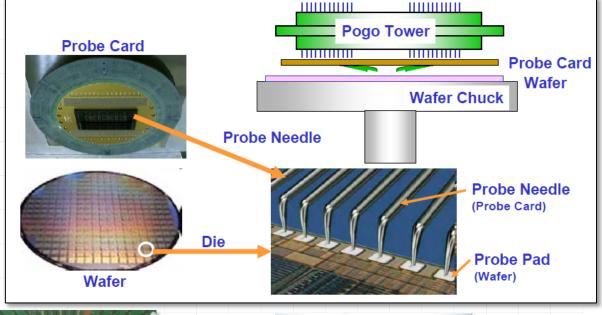

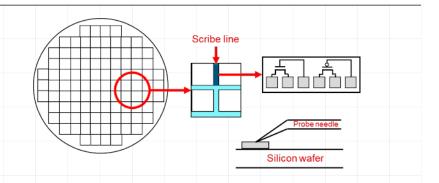

# Mission of Probe is Critical Data

Image Source: Verigy

#### THREE PRIMARY COMPONENTS of a TEST CELL

- **1. ATE**: Instruments & power supplies that stimulate and interrogate the DUT(s).

- **2. Probe card**: Device-specific interface that provides the electromechanical DUT-to-ATE contact.

- **3. Prober**: device wafer handling, positioning, thermal environment, and probe cleaning.

Feedback to FAB for Manufacturing

Reliable Data to Improve Design

**Categorize Devices on Performance**

Maintain High Yields to Avoid Retest

Facilitate Multi-Die "KGD" Solutions

**Reduce Yield Loss at Final Test**

Test Provides Metrology For Entire Semiconductor Value Chain

Source: Ozawa, SWTest Asia 2019 Keynote, J. Broz, IEEE CISTIC 2020 Virtual

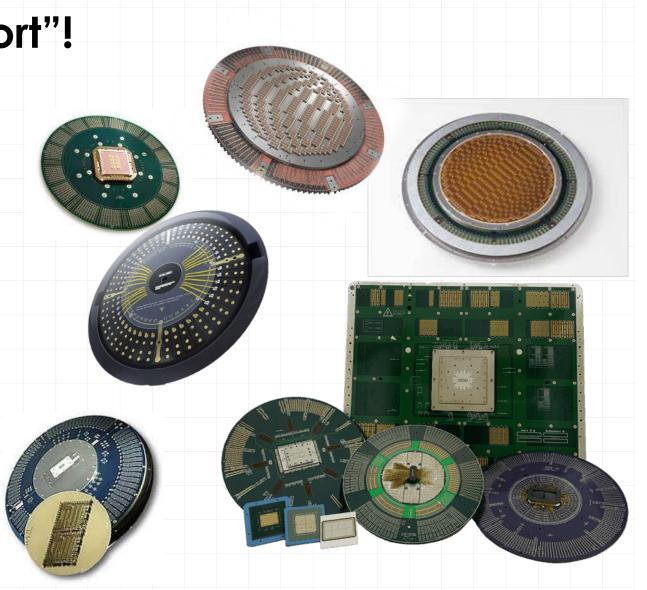

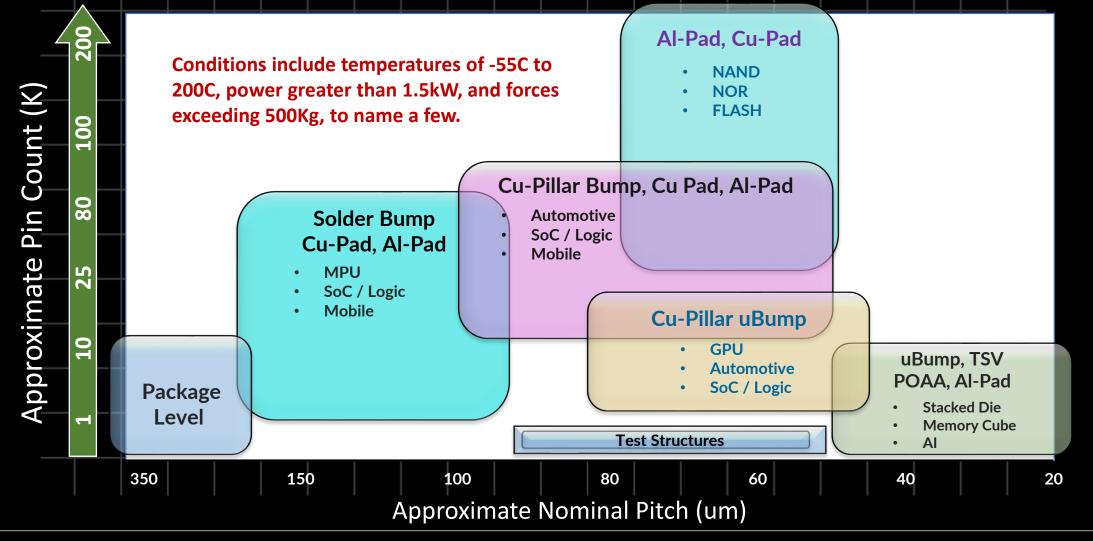

# Probing is a "Contact Sport"!

- Physical contact by small diameter probes onto the I/Os of individual DUTs.

- Electrical contact to execute various functional tests to determine the "goodness" of the device.

- Parametric test with low leakage, fast settling times, low cross-talk, guarded traces, temperatures from -55C to 200C.

- Production level memory and nonmemory probe-cards are highly specialized for every application.

# Probing is a "Contact Sport"!

- Physical contact by small diameter probes onto the I/Os of individual DUTs.

- Electrical contact to execute various functional tests to determine the "goodness" of the device.

- Parametric test with low leakage, fast settling times, low cross-talk, guarded traces, temperatures from -55C to 200C.

- Production level memory and nonmemory probe-cards are highly specialized for every application.

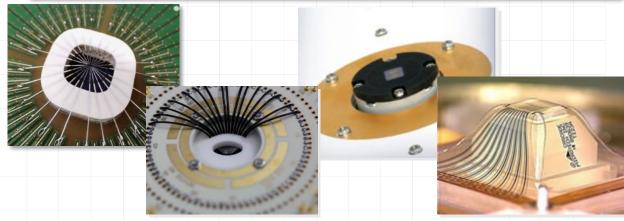

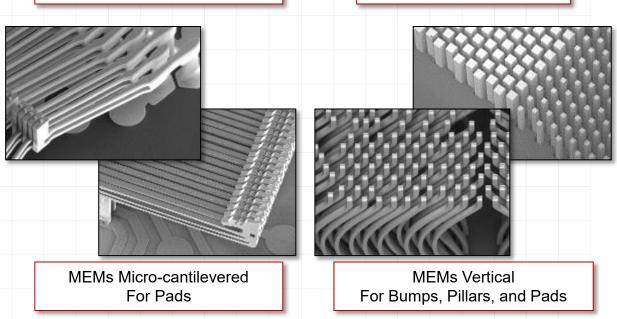

# **Probes Make the "Contact"**

### IC – Cantilevered Wire Probe

- Small diameter Tungsten, Tungsten Rhenium, BeCu wire probes mounted on a PCB.

- Pin count range: tens up to several thousand.

### IC - Vertical Probe

- Buckling beams, wired, or spring probes controlled using various guide plates.

- Pin in count range: several thousand to more than 50K.

### • IC - MEMS Probe

- 3D MEMS : entire card (or tile) of multiple contacts are created as a single processed unit.

- 2D MEMS : litho and etch processes to manufacture individual probe structures mounted onto a substrate.

- Pin count range: several thousand to more than 200K.

Cantilevered Probes For Pads

Vertical Spring Pins For Bumps and Pillars

### Gel-Pak ТоиснМакк UltraTape

# No SINGLE Probe Card Type Fits ALL Test Requirements!

A Delphon Company

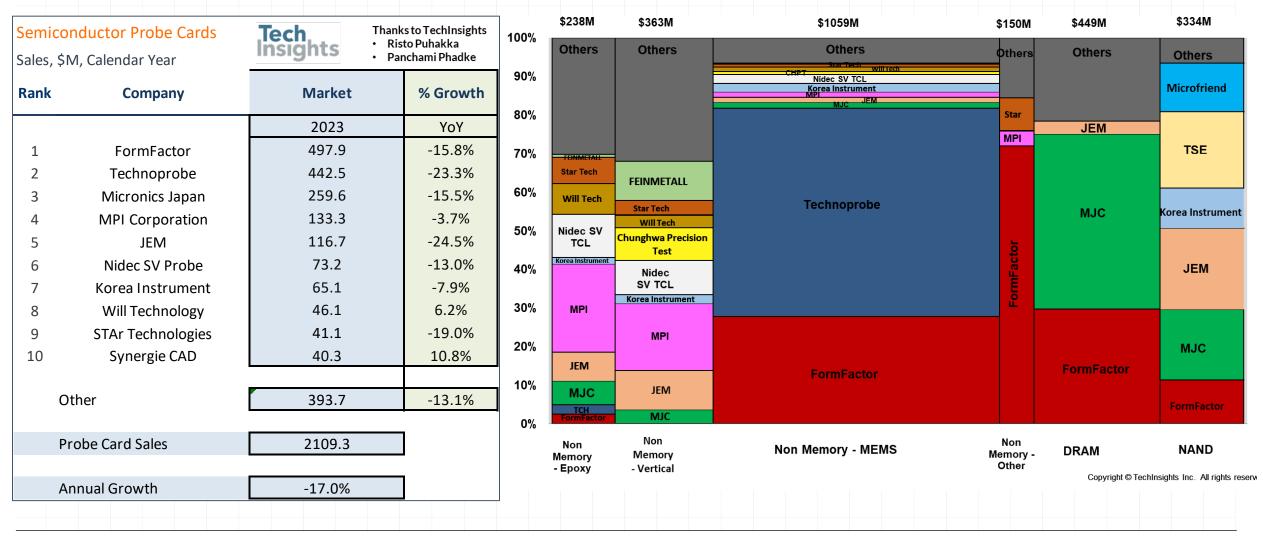

# **Diverse Probe Card Landscape (2023)**

A Delphon Company

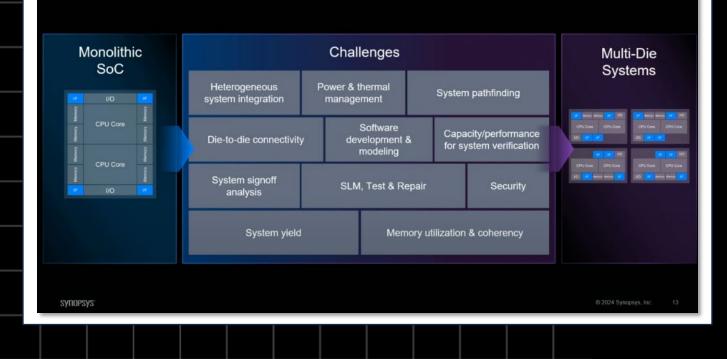

# Value of Probe Increases for Multi-die Packages

- Continuing with a "monolithic" approach has extremely high development costs.

- Materials and structural innovations have long development cycle times.

- Heterogeneous integration and advanced uses "best-in-class IP" from multiple sources to advance performance at acceptable costs.

Multi-Die Systems Have New Challenges

### Multi-Die Strategies Demand "KGD" (or "Not Bad") Solutions

Source: TSMC Open Innovation Platform® Ecosystem Forum 2019

Gel-Pak TouchMark UltraTape 26

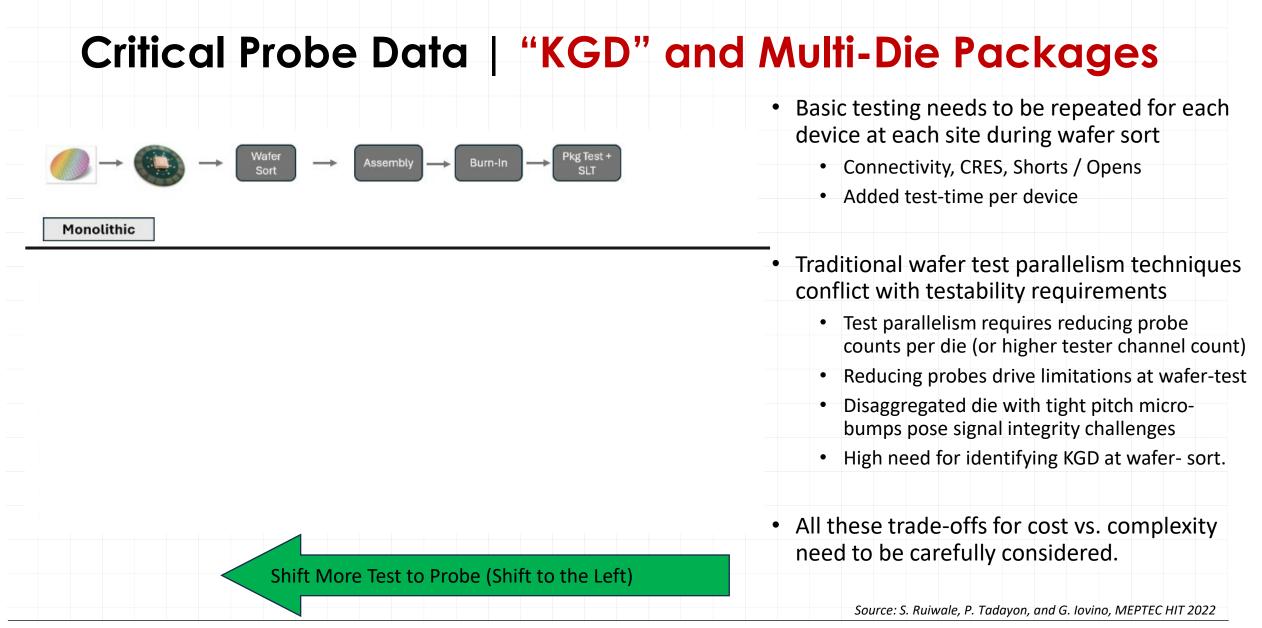

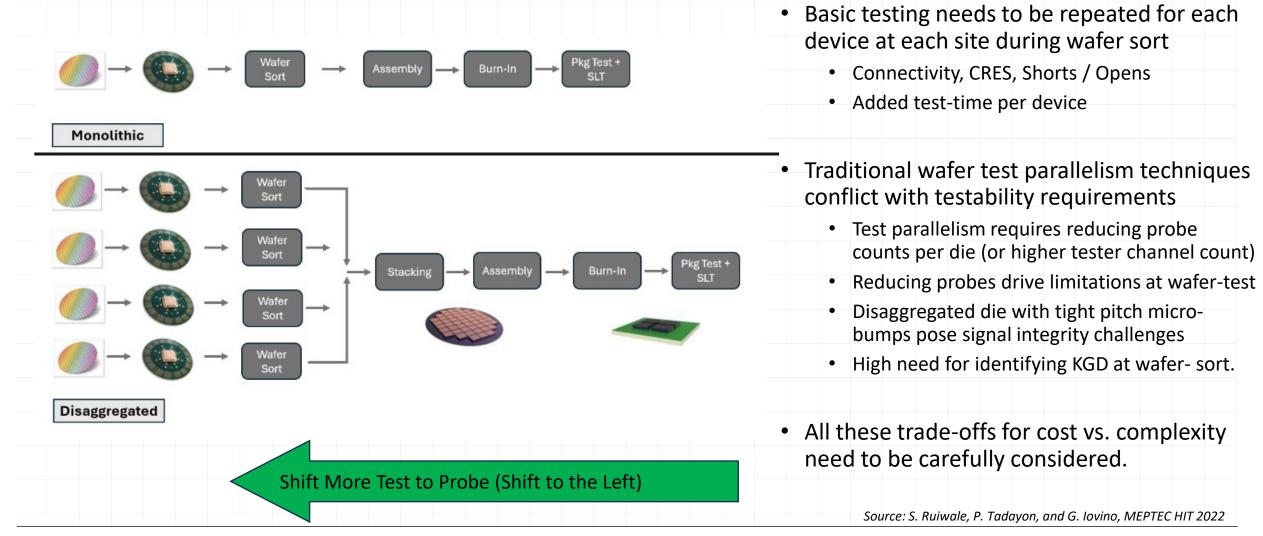

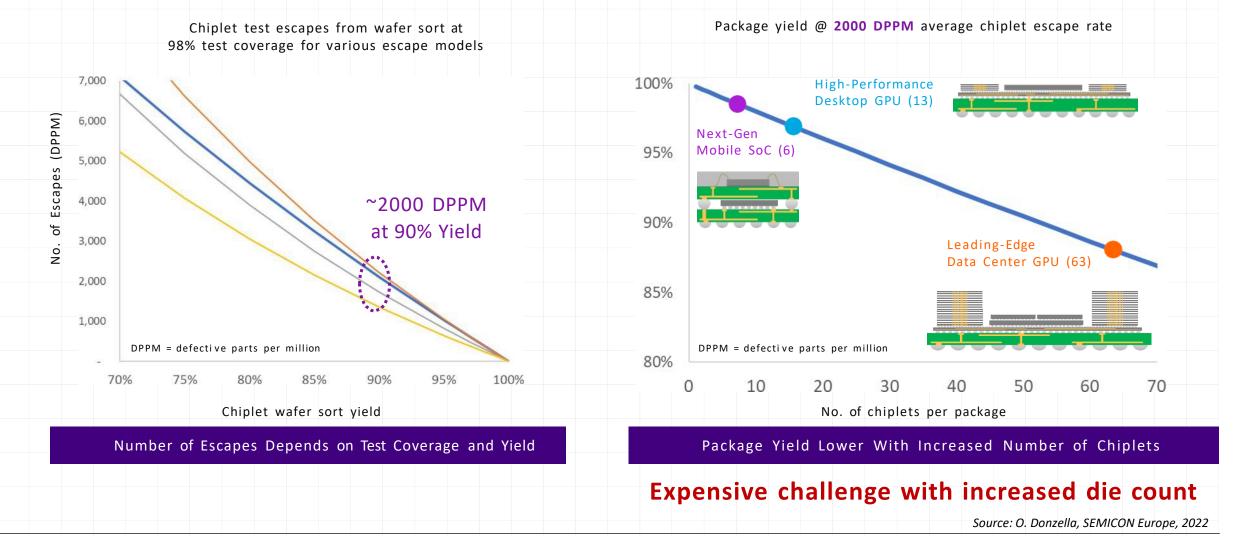

# Critical Probe Data | "KGD" and Multi-Die Packages

#### UltraTape **TOUCHMARK** 27 Gel-Pak

# Critical Probe Data | "KGD" and "Not-Bad" Die

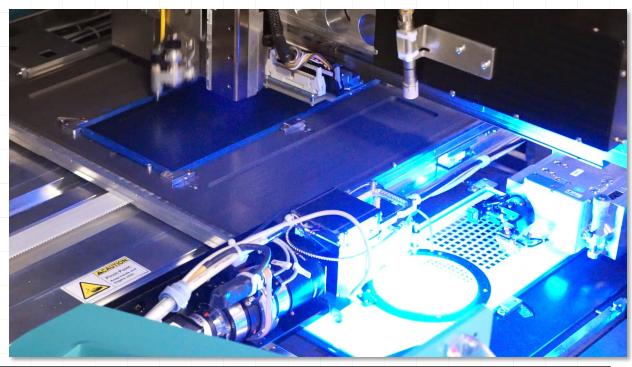

# "Shift to the Left" | New Probe Strategies

- 1. New probing technologies must facilitate cost efficient test of singulated die and stacks of die.

- 2. Wafer prober, test cell, and devices handlers to support singulated die.

- 3. Cost effective methods to universally handle numerous die sizes after saw, thin, and bump.

- 4. Reduce scrapped die due induced defects (saw, thin, bump, etc.) in shared assemblies.

- Significant work underway to allow die to be reassembled in silicon panels that have a rectangular shape as opposed to the round shape of the original silicon wafer.

- Universal / Pocketless Tray Formfactor

- Minimal Contact with Devices

- Optimal Holding Force

# "Shift to the Left" | New Probe Strategies

- 1. New probing technologies must facilitate cost efficient test of singulated die and stacks of die.

- 2. Wafer prober, test cell, and devices handlers to support singulated die.

- 3. Cost effective methods to universally handle numerous die sizes after saw, thin, and bump.

- 4. Reduce scrapped die due induced defects (saw, thin, bump, etc.) in shared assemblies.

- Significant work underway to allow die to be reassembled in silicon panels that have a rectangular shape as opposed to the round shape of the original silicon wafer.

- Universal / Pocketless Tray Formfactor

- Minimal Contact with Devices

- Optimal Holding Force

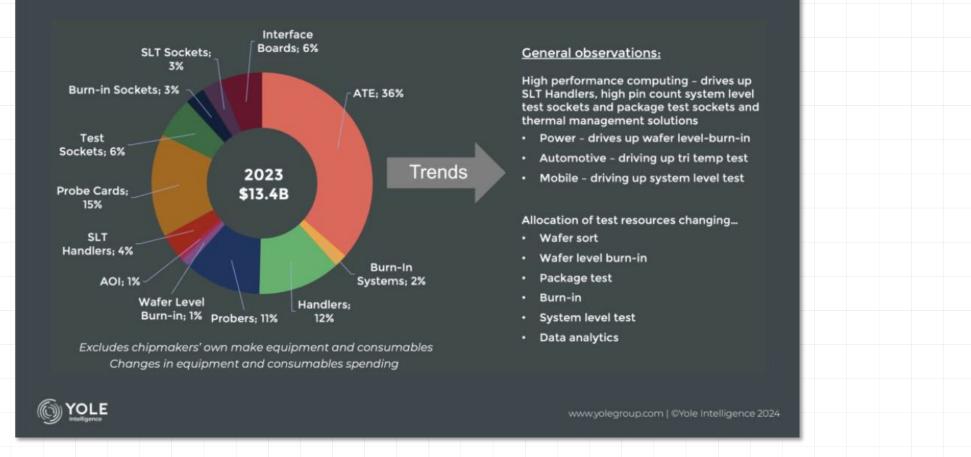

# Increased Cost of Test | Test Equipment Landscape

#### **TEST EQUIPMENT MARKET – OVERALL 2023 COST**

Source: Semiconductor Test Equipment Market Monitor & Semiconductor Test Consumables Market Monitor, Q1 2024, Yole Intelligence

A Delphon Company

Gel-Pak ТоиснМакк UltraTape

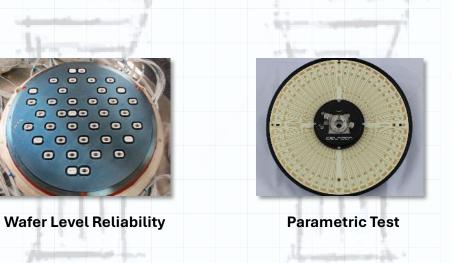

# Lab to Fab

- **Device Characterization** •

- **Design Validation**

- **High Power**

- **RF-mmW**

- Wafer Level Reliability

**Engineering Probing**

**Engineering Labs**

Failure Analysis ٠

Modeling / Characterization

**Device Labs**

**Modeling Labs**

**Characterization Labs**

- Data extraction and analysis are crucial ٠ from test lab to fab manufacturing.

- Each phase produces vital information ٠ for successive phases.

- Insights gained in the lab are critical for efficiency on the production floor.

0

**Burn-In Labs**

**Reliability Labs**

**High Volume Manufacturing**

0 0

> **Device Labs First Silicon Analysis High Volume Manufacturing**

# Lab to Fab | Critical Data

- Critical Data Targets: maximize production yields by identifying potential issues early in the process.

- Parametric Test & Structures

- Located in the region between adjacent die.

- Vary within the scribelines and stability of the silicon process.

- Provides the data to judge whether silicon process is in control.

- No 1:1 correlations between product die and parametric test results.

- Basic electrical characteristics on the wafer:

- Transistor threshold voltage

- Leakage current

- Capacitance

- Resistance

- Diode Characteristics

- Parametric tests evaluate the wafer fab's process capability of yielding product die and monitor the health of a factory as a function of time and material.

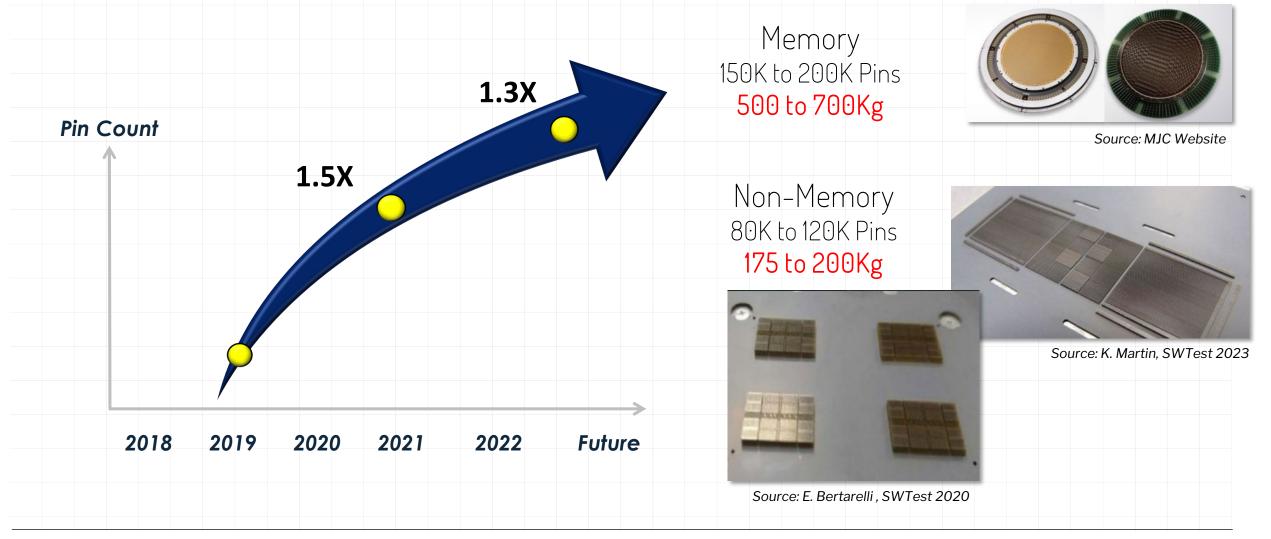

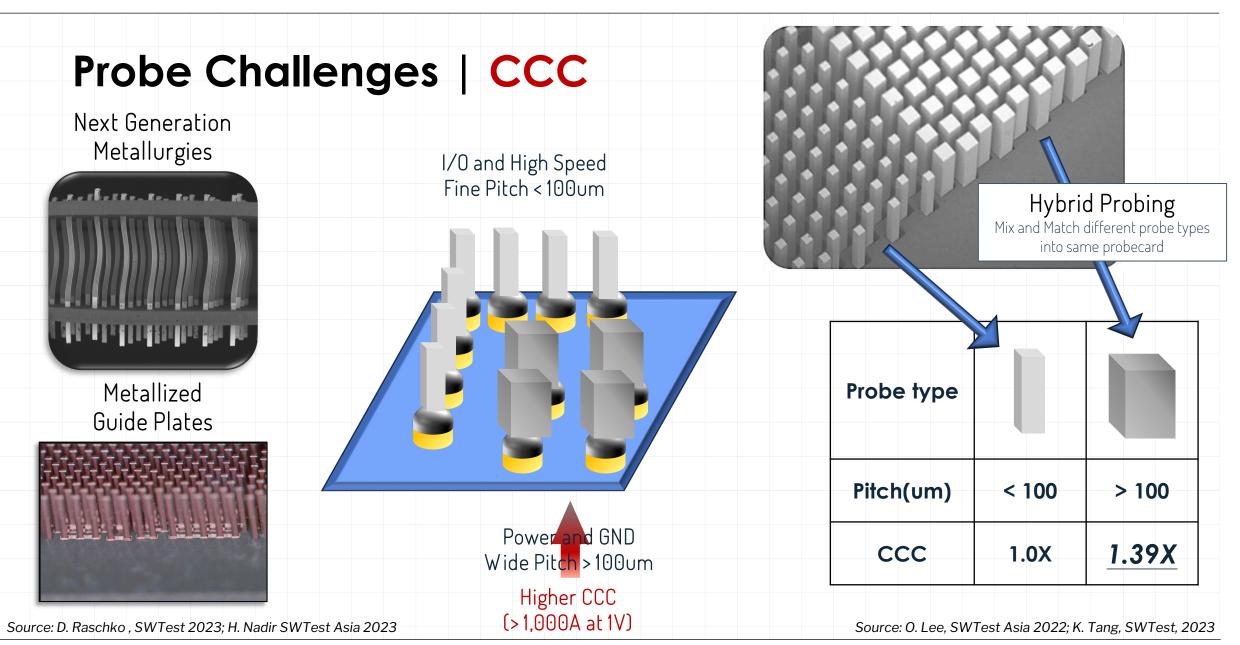

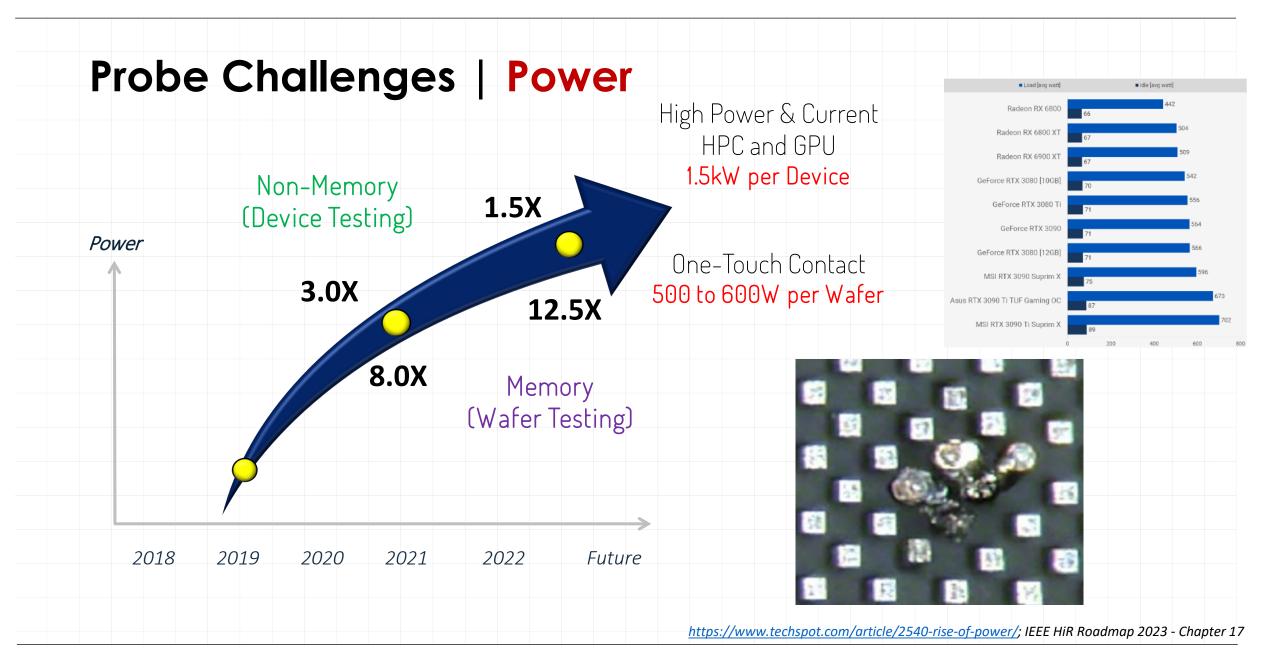

# Lab to Fab Challenges | Probe Scaling

- Minimum Pad Size: 30um x 30um

- Contact Resistance: <1 ohm</li>

- Temperature: -65C to +200C

- Lifetime performance: +10M TDs

- DRAM: 1-TD, X2000 DUT, >175K probes @ 60um pitch

- Logic: X16 DUT, >80K probes @ 75um pitch

- Temperature: -40C to 175C

- Lifetime performance: 100K to 2M TDs

### A Delphon Company

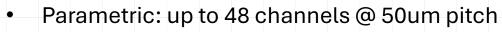

# Probe Challenges | High Pin Counts

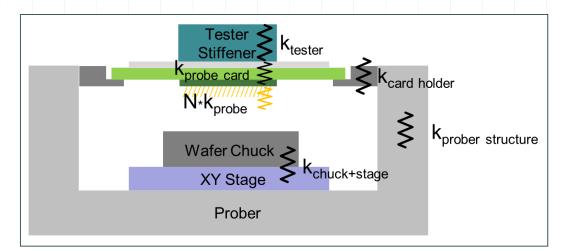

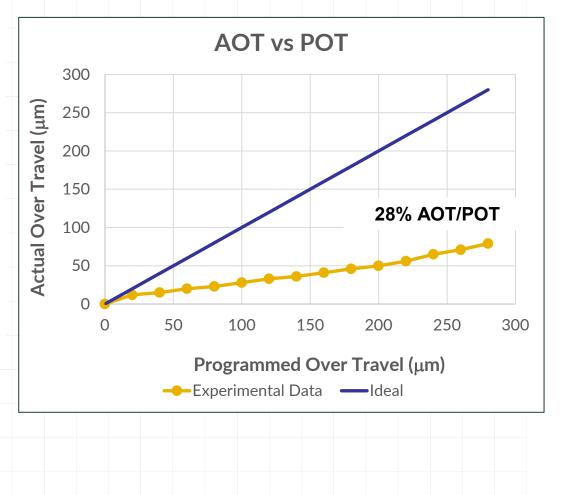

# Probe Challenges | AOT vs. POT

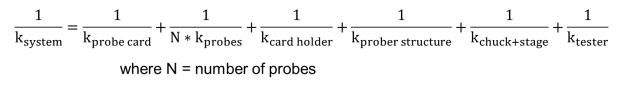

The system consists of a group of springs in series:

Actual compression of the probes is less than programmed due to non-infinite system stiffness.

Source: K. Martin, SWTest 2023

Source: T. Berry. K. Breinlinger, R. Rincon, SWTest, 2012

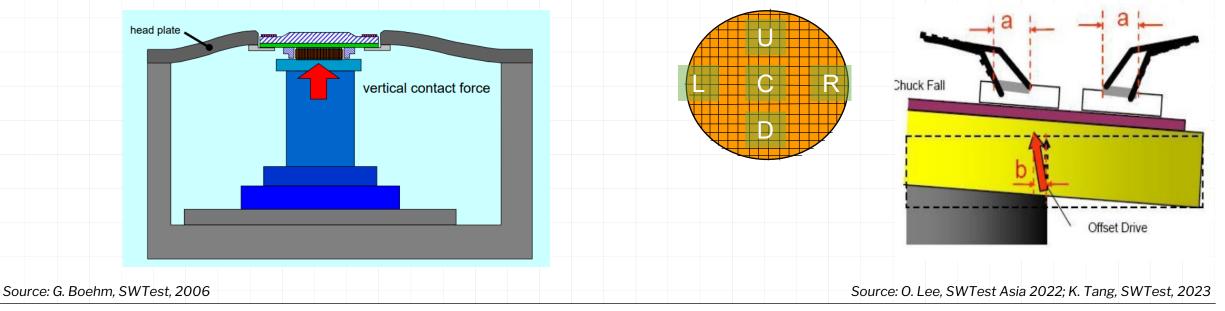

# Probe Challenges | Contact Force

- Probers need high force wafer chuck options pushing the limits to more than 700 kg.

- 200K probes at 2.5 gf each

- > 500 kg total force!

- High pin count probe card, the significant decrease in AOT is the system deformation.

- Probers need minimal chuck deflection during offset high force loading condition

- 80k probes at 2.5 gf each

- > 200 kg off-set total force!

- Non-uniform AOT is observed with offset loading using high pin count arrays.

### Probe Challenges | Probers, Interfaces, and Testers

Accretech AP3000 Prober Accretech AltaProv Modular Prober Advantest DUT Scale Duo Tester AltaPro AP3000 **TEL Prexa Prober** TEL Cellcia Modular Prober Teradyne UltraFLEXplus Tester TEL TEL Test System 1

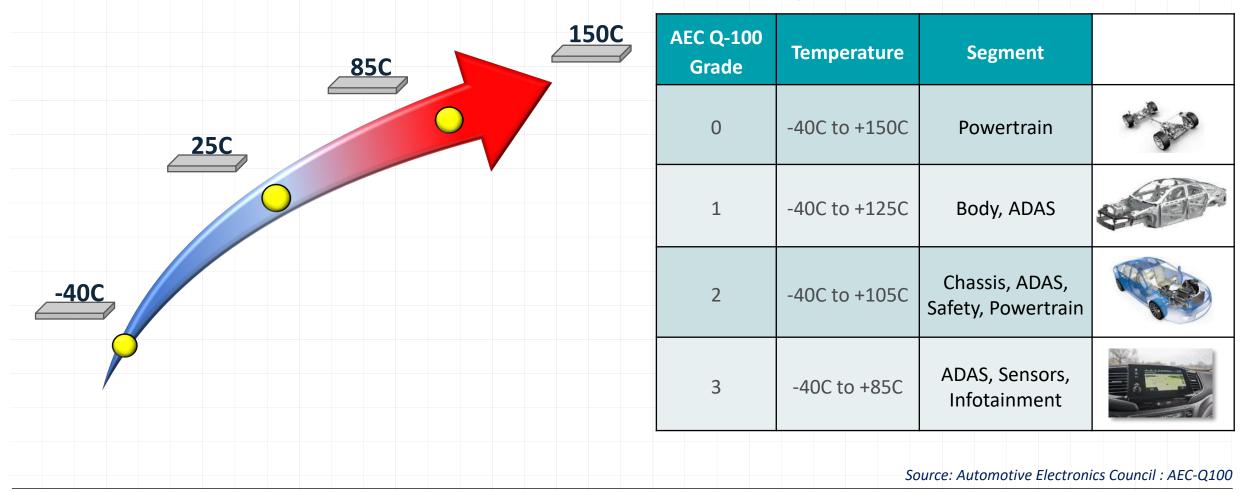

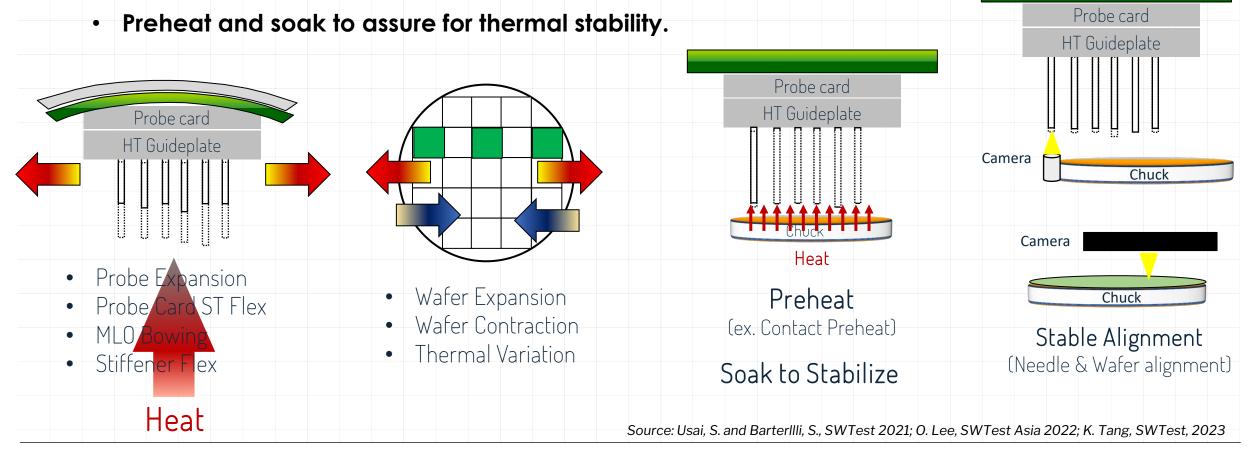

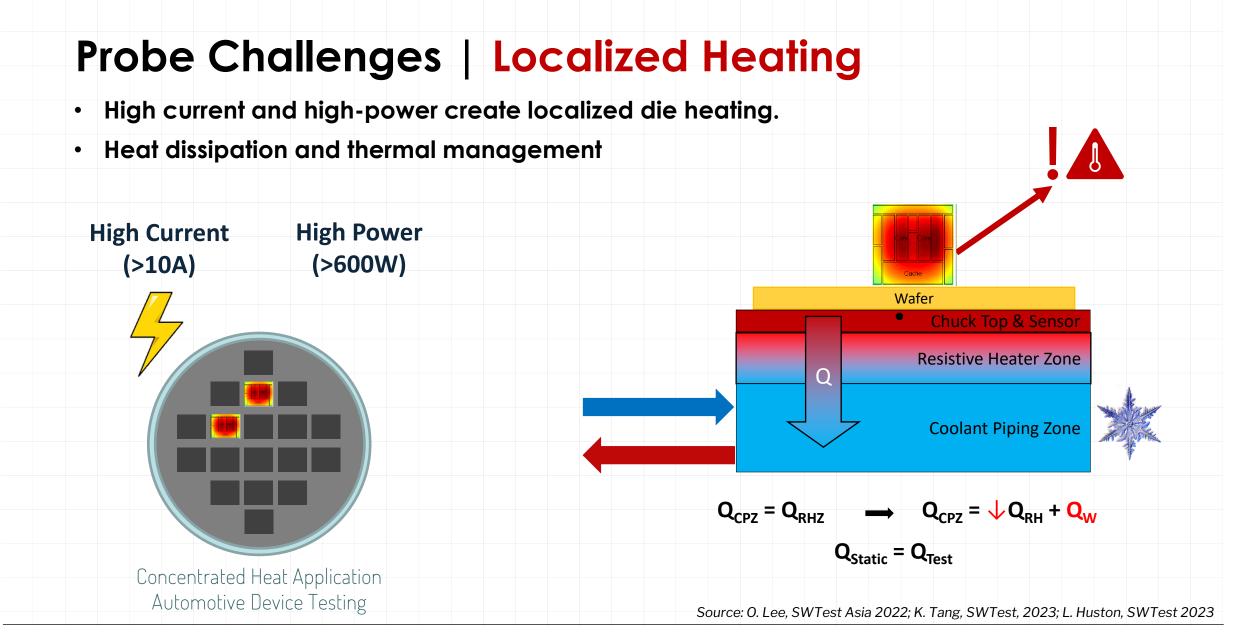

### Probe Challenges | Temperature

Demanding Automotive Reliability Requirements

### Probe Challenges | CTE Mismatch

CTE (Coefficient of Thermal Expansion) mismatches cause deformations and affect probe-to-pad and probe-to-bump misalignment.

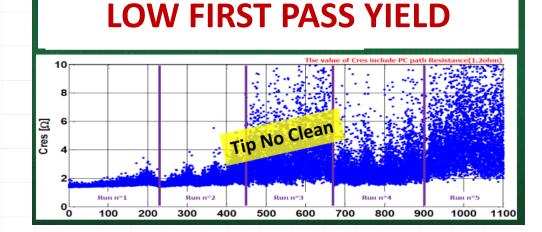

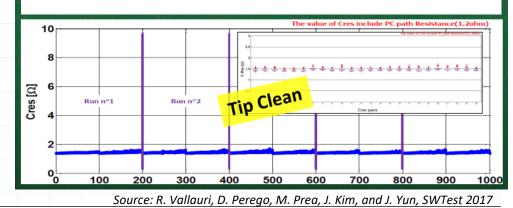

# Probe Challenges | Contact & Lifetime (Cleaning)

Film

Resistance

Probes touch the DUT, but the Current Might NOT Flow !

- Probe cleaning is a "dirty business" and critical for controlling contact.

- Cleaning can consume more 95% of a probe card lifetime.

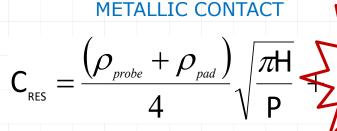

- $\rho_{pad}, \rho_{probe}, \sigma_{film}$  = resistivity values

- H = hardness of the pads, bumps, pillars, etc.

- P = contact pressure applied by probe

Implement efficient cleaning

to ensure reliable electrical contact.

### **HIGH FIRST PASS YIELD**

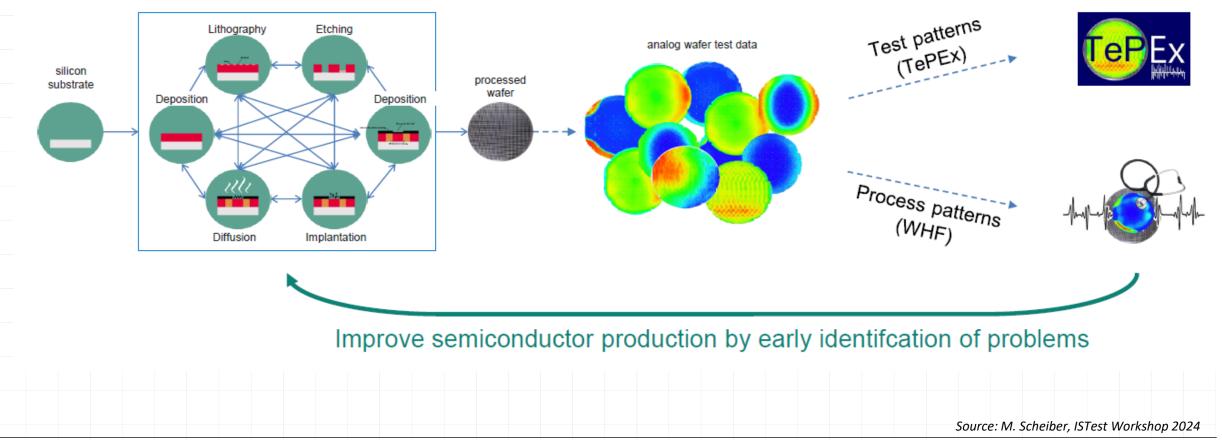

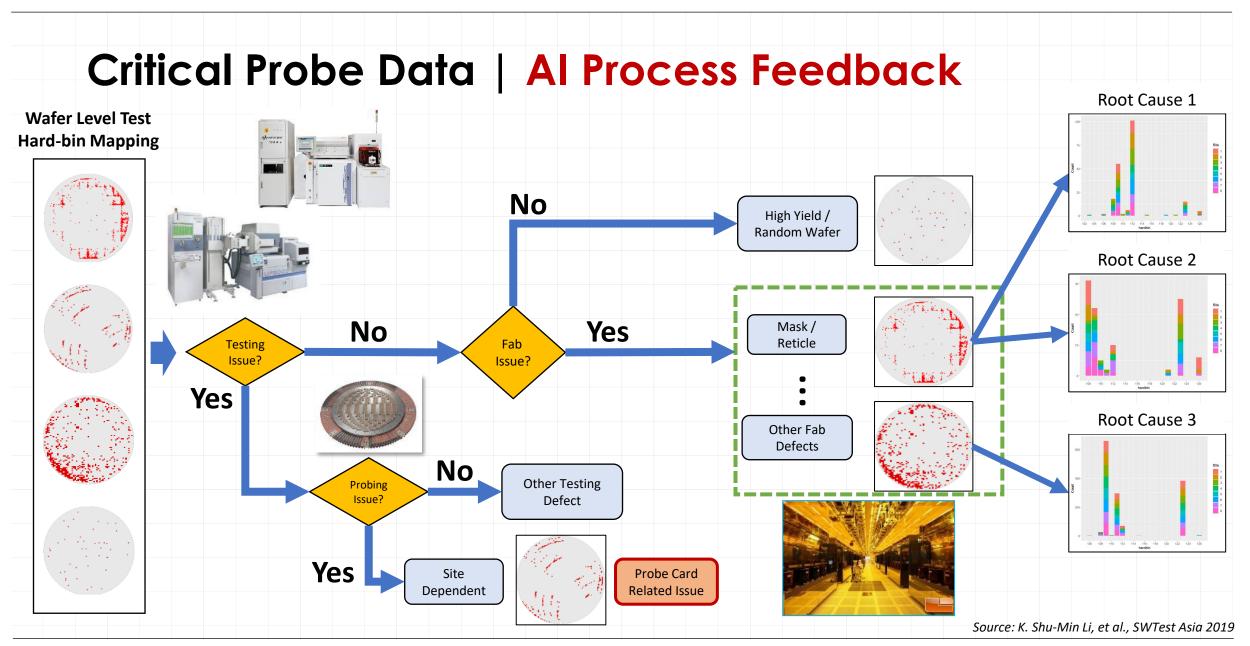

### Critical Probe Data | Al Analysis for FAB

Gel-Pak ТоиснМакк UltraTape

# Summary and Takeaways

2<sup>nd</sup> Tier IDMs, foundries, and OSATs must rely more heavily on test thoroughness going from the Lab to the Fab.

Significant challenges are emerging that require technical partnerships to economically address the demands of increased test coverage, increased complexity and data quality.

Wafer probe must not become a limiter for new technologies and multisupplier, collaborative innovation is clearly necessary to enable costeffective, optimized strategies.

### Where to Learn About Probe Challenges? | SWTest Conferences

SWTest 2025 San Diego

June 2 to 4, 2025 Omni La Costa, California

SWTest Asia 2025 Fukuoka

November 20 to 22, 2025 Hilton Sea Hawk, Fukuoka, Japan

#### **SWTest Conferences**

### PROBE TODAY, FOR TOMORROW

# SWTest Asia 2025 | Fukuoka, Japan

- Schedule : November 20 22, 2025

- Location : Hilton Fukuoka Sea Hawk

- Conference Day 1 (Nov. 20, 2025)

- Opening and Visionary Keynote

- Podium Sessions & Poster Sessions

- Key Supplier Expo

- Platinum Sponsor Tech-Showcase

- Networking Event in Expo Hall

#### • Conference Day 2 (Nov. 21, 2025)

- Opening

- Podium Sessions & Poster Sessions

- Key Supplier Expo

- Platinum Sponsor Tech-Showcase

- Networking Event

#### • Charity Golf Tournament and Networking Day 3 (Nov. 22, 2025)

• Benefit Golf Tournament to support student participation.

PROBE TODAY, FOR TOMORROW

# Achnowledgements

- Victoria Tran, PhD R&D Director at Delphon

- Rajiv Varma CTO at Delphon

- Joseph Montano CEO at Delphon

# DELPHON

Merging Innovative Technologies

# Increasing the Role of Probe from Lab to Fab: The Mission of Critical Data

### Jerry Broz, PhD

VP of Business Development & Strategic Marketing, Delphon Industries, LLC. General Chair of SWTest Conferences